ORGANISASI PROCESSOR

1.Perhatikan mekasisme

dan persyaratan yang terdapat pada CPU

2.Aktivitas yang dilakukan

CPU Apa saja ????

Aktivitas CPU :

- Mengambil

Instruksi/Fetch Instruction

- Interpret Instruksi

- Mengambil

Data/Fetch Data

- Mengolah

Data/Process Data

- Menulis Data/Write

Data

CPU vs TUGAS

- Agar dapat melaksanakan

tugas, CPU harus:

- CPU menyimpan data untuk

sementara waktu

- CPU harus mengingat

lokasi instruksi terakhir sehingga CPU akan dapat mengambil instruksi berikutnya

- CPU perlu menyimpan

dan instruksi dan data untuk sementara waktu pada saat instruksi sedang di

eksekusi

- CPU memerlukan memory

internal berukuran kecil yang dikenal dengan REGISTER

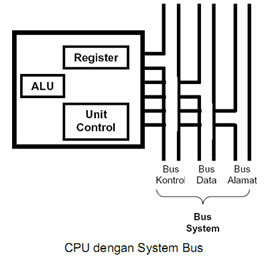

Komponen Utama CPU

- Arithmetic and

Logic Unit (ALU)

- Control Unit

- Registers

- CPU Interconnections

Arithmetic and Logic Unit (ALU)

- Bertugas membentuk

fungsi – fungsi pengolahan data komputer.

- ALU sering disebut

mesin bahasa ( machine language) karena bagian ini mengerjakan instruksi –

instruksi bahasa mesin yang diberikan padanya. Seperti istilahnya

- ALU terdiri dari dua

bagian, yaitu unit arithmetika dan unit logika boolean, yang masing – masing

memiliki spesifikasi tugastersendiri.

Control Unit (CU)

- Bertugas mengontrol

operasi CPU dan secara keselurahan mengontrol komputer sehingga terjadi

sinkronisasi kerja antar komponen dalam menjalankan fungsi –fungsi operasinya.

- Termasuk dalam

tanggung jawab unit kontrol adalah mengambil instruksi – instruksi dari memori

utama dan menentukan jenis instruksi tersebut.

Registers

- Media penyimpan

internal CPU yang digunakan saat proses pengolahan data.

- Memori ini bersifat

sementara, biasanya digunakan untuk menyimpan data saat diolah ataupun data

untuk pengolahan selanjutnya.

CPU Interconnections

- Sistem koneksi dan

bus yang menghubungkan komponen internal dan bus -bus eksternal CPU

- Komponen internal

CPU yaitu ALU, unit kontrol dan register – register.

- Komponen eksternal CPU

:sistem lainnya, seperti memori utama, piranti masukan/keluaran

ORGANISASI REGISTER

- Sistem komputer

menggunakan hirarki memori

- Pada tingkatan yang

atas, memori yang lebih cepat, lebih kecil, dan lebih mahal (per bit)

- Didalam CPU

terdapat sekumpulan Register yang tingkatan memorinya berada diatas hirarki

memori utama dan cache.

Apa fungsi register

pada CPU ?

Fungsi Register CPU

- User

visible-Register

- Register ini

memungkinkan programmer bahasa mesin dan bahasa assembler meminimalkan

referensi main memory dengan cara mengoptimasi penggunaan register

- Control &

Status Register

- Register ini

digunakan oleh unit kontrol untuk mengontrol operasi CPU dan oleh program

sistem operasi untuk mengontrol eksekusi program

- Tidak terdapat

pemisahan yang jelas antara kedua jenis register di atas.

User Visible Register

adalah register yang

dapat direferensikan dengan menggunakan bahasa mesin yang dieksekusi CPU.

Kategorinya :

·

General Purpose

·

Data

·

Alamat

·

Kode-kode Kondisi

* General-purpose

register dapat digunakan untuk berbagai fungsi oleh pemrogram.

* General-purpose

register dapat dapat berisi operand sembarang opcode.

* Pada kasus-kasus

tertentu, general-purpose register dapat digunakan untuk fungsi-fungsi

pengalamatan (misalnya, register indirect, displacement)

* Pada kasus lainnya,

terdapat partial atau batasan yang jelas antara register data dengan register

alamat.

Register Data dan Alamat

- Register data hanya

dapat dipakai untuk menampung data dan tidak dapat digunakan untuk kalkulasi

dan alamat operand.

- Register alamat

menyerupai general-purpose,atau register-register tersebut dapat digunakan

untuk mode pengalamatan tertentu

- Contohnya : Segment

pointer, Register Index, Stack pointer

- Segment Pointer,

· Register segmen menyimpan alamat berbasis segmen.

· Mungkin terdapat beberapa register, misalnya satu register untuk sistem

operasi dan satu register untuk proses saat itu

Register Index,

·

Untuk alamat-alamat yang terindeks dan mungkin autoindexed

Stack Pointer,

·

apabila terdapat pengalamatan stack yang user-visible, maka biasanya

stack berada di dalam memori dan terdapat register dedicated yang menunjuk ke

bagian atas stack.

·

Memungkinkan pengalamatan implisit, yaitu push, pop, dan instruksi stack

lainnya tidak perlu operand stack eksplisit.

Masalah

- Apakah perlu

menggunakan general-purpose register seluruhnya atau hanya untuk

keperluan-keperluan khusus saja ?

- Jumlah register

yang harus tersedia, baik general-purpose maupun register data dan register

alamat.

Sharing (1)

- Specifer operand hanya

perlu mengidentifikasi salah satu kumputer register khusus saja, dan tidak

perlu mengidentifikasi seluruhnya, karena itu akan dapat menghemat bit

- Khususan ini membatasi

flesibilitas pemograman

- Tidak terdapat solusi

akhir bagi masalah rancangan ini, namun seperti telah dinyatakan di atas,

kecenderungan mengarah ke penggunaan register yang khusus

Sharing (2)

- Jumlah register

sangat menentukan kinerja suatu prosesor.

- Jumlah register

juga berpengaruh pada rancangan set instruksi karena register yang lebih banyak

akan memerlukan bits operand specifier yang lebih banyak pula.

- Register yang

berukuran antara 8 hingga 32 dapat dikatakan optimum.

- Register yang

jumlahnya lebih sedikit akan menghasilkan referensi memori yang lebih banyak,

register yang lebih banyak tidak akan mengurangi jumlah refrensi memory

secara berarti.

Control and Status Register

Bermacam-macam register

CPU yang digunakan untuk mengontrol operasi CPU

* “Non Visible” vs

“Visible“

·

Tidak visibel bagi pengguna

·

Visibel terhadap instruksi mesin yang di eksekusi pada model control sistem

operasi

Register yang penting bagi eksekusi

instruksi

- Program Counter

(PC) atau Pencacah Program

·

berisi alamat instruksi yang akan diambil.

- Instruction

Register (IR)

·

berisi instruksi yang terakhir diambil.

- Memori Address Register

(MAR)

·

berisi alamat sebuah lokasi di dalam memori.

- Memori Buffer

Register (MBR)

·

berisi sebuah word data yang akan dituliskan ke dalam memori atau word

yang terakhir dibaca.

Program Status Word (PSW)

adalah semua

rancangan CPU mencakup sebuah register atau sekumpulan register

- Berisi informasi

status

- Berisi kode kondisi

dan informasi status lainnya

Common field atau flag, Apa saja?

Sign

·

Berisi bit tanda hasil operasi aritmetika terakhir, negatif atau positf

Zero

·

Diset bila hasil sama dengan nol

Carry

·

Diset apabila operasi yang dihasilkan di dalam carry (penambahan) ke

dalam bit yang lebih tinggi atau borrow ( pengurangan pengurangan) dari bit

yang lebih tinggi.

·

Digunakan untuk operasi aritmetika multiword

Common field atau flag, Apa saja ?

Equal

·

Diset apabila hasil logika perbandingan sama.

Overflow

·

Identifikasikan overflow aritmatika.

Interrupt

Enable/Disable

·

Status ijin terhadap interupt.

Supervisor

·

Mode previleged (ex. mode supervisor/user)

SIKLUS INSTRUKSI

*Ada beberapa

sub-siklus

* Apa saja?

Sub-siklus instruksi

Fetch

·

Adalah siklus pengambilan data ke memori

atau register

Execute

·

Menginterpretasikan opcode dan melakukan operasi yang diindikasikan

Interrupt

·

Apabila interrupt diaktifkan dan interrupt telahterjadi,ssimpan status proses saat itu dan layani interuksi

Siklus Tidak Langsung, Apa itu?

- Eksekusi sebuah

instruksi melibatkan sebuah operand atau lebih di dalam memori, yang

masing-masing operand memerlukan akses memori

- Pengambilan

alamat-alamat tak langsung langsung dapat dianggap sebagai sebuah sebuah

subsiklus instruksi atau lebih

Sifat-siklus instruksi

- Sekali instruksi

telah diambil, maka operand specifier-nya harus diidentifikasikan.

- Kemudian seluruh

operand input yang berada di dalam memori akan diambil, dan proses ini mungkin

memerlukan pengalamatan tak langsung.

- Operand berbasis

register tidak perlu diambil.

- Apabila opcode

telah dieksekusi, proses yang sama akan diperlukan untuk menyimpan hasilnya di

dalam memori

Diagram status siklus instruksi

Aliran data siklus pengambilan

Aliran data siklus tak langsung

Strategi Pipelining

- Pipelining, Apa itu

?

·

Inut baru akan diterima pada sebuah sisi sebelum input yang diterima

sebelumnya keluar sebagai output di sisi lainnya

- Pendekatan :

·

Pipelining instruksi mirip dengan penggunaan rangkaian perakitan pada

pabrik.

·

Rangkaian perakitan memanfaatkan kelebihan yang didapat dari fakta bahwa

suatu produk diperoleh dengan melalui berbagai tahapan produksi.

·

Dengan menaruh proses produksi di luar rangkaian perakitan, maka produk

yang berada diberbagai tahapan dapat bekerja secara bersamaan.

Pipeline instruksi dua tahap

Pipeline ? Pengolahan instruksi

1. Pengambilan

instruksi (Fetch)

2. Pengeksekusian instruksi (Execute)

2. Pengeksekusian instruksi (Execute)

3. Terdapat waktu yang

dibutuhkan selama proses eksekusi sebuah instruksi pada saat memori sedang

tidak diakses.

4. Waktu ini dapat

digunakan untuk mengambil instruksi berikutnya secara paralel (bersamaan)

dengan eksekusi instruksi saat itu.

Tahapan Pipeline

- Tahapannya

Independen

- Mengapa ?

·

Tiap tahapan bekerja sendiri

·

Kedua bekerja dalam waktu yang bersamaan

- Ada berapa ?

Ada 2 tahap :

- Tahapan pertama

mengambil instruksi dan mem-buffer-kannya.

- Ketika tahapan

kedua bebas, tahapan pertama mengirimkan instruksi yang di-buffer-kan tersebut.

- Pada saat tahapan

kedua sedang mengeksekusi instruksi, tahapan pertama memanfaatkan siklus memori

yang tidak dipakai untuk mengambil dan membufferkan instruksi berikutnya.

·

Proses ini disebut instruction prefetch atau fetch overllap

Efek Pipeline

- Mempercepat

eksekusi instruksi.

- Apabila tahapan

pengambilan dan eksekusi instruksi memerlukan waktu yang sama, maka siklus

instruksi akan berkurang menjadi separuhnya

- Penggandaan

kecepatan eksekusi tidak akan terjadi apabila beberapa hal terjadi

- Apa saja alasannya

?

- Bagaimana

mengatasinya ?

Alasan ?

- Umumnya waktu

eksekusi akan lebih lama dibandingkan dengan pengambilan instruksi. Kenapa ?

Eksekusi akan meliputi pembacaan dan penyimpanan operand serta kinerja sejumlah

operasi sehingga tahapan pengambilan mungkin perlu menunggu beberapa saat sebelum

mengosongkan buffer-nya

- Instruksi

pencabangan bersyarat akan membuat alamat instruksi berikutnya yang akan

diambil tidak diketahui. Tahapan pengambilan harus menunggu sampai menerima

alamat instruksi berikutnya dari tahapan eksekusi. Dengan demikian tahapan

eksekusi harus menunggu pada saat fetch

Solusi

- Kerugian waktu yang

diakibatkan tahapan kedua (Pencabangan bersyarat) dapat dikurangi dengan cara :

Menebak = Prediksi

Aturan Prediksi ?

Aturannya sederhana

- Instruksi

pencabangan bersyarat dikirimkan dari tahapan pengambilan ke ahapan eksekusi,

tahapan pengambilan mengambil instruksi berikutnya di dalam memori setelah

terjadinya instruksi pencabangan itu.

- Apabila pencabangan

tidak dilakukan, maka tidak akan terdapat waktu yang hilang.

- Apabila pencabangan

dilakukan, instruksi yang diambil harus dibuang dan instruksi yang baru harus

di ambil

- Faktor-faktor di

atas mengurangi efektivitas pipeline dua tahap, namun terjadi juga beberapa

percepatan.

- Untuk memperoleh

percepatan lebih lanjut, pipeline harus memiliki lebih banyak tahapan

Dekomposisi pengolahan instruksi

* Fetch Instruction

(FI)

·

membaca instruksi berikutnya ke dalam buffer

* Decode Instruction

(DI)

·

menentukan opcode dan operand specifier

* Calculate Operand

(CO)

·

menghitung alamat efektif seluruh operand sumber. Hal ini mungkin

melibatkan displacement, register indirect, atau bentuk kalkulasi alamat

lainnya

* Fetch Operand (FO)

· mengambil semua operand dari memori. Operand-operand yang berada di

register tidak perlu diambil

* Executte

Instruction (EI)

·

melakukan operasi yang diindikasikan dan menyimpan hasilnya

* Write Operand (WO)

·

menyimpan hasilnya di dalam memori

Efek dekomposisi diatas apa ?

- Bermacam tahapan

dapat memiliki durasi yang hampir sama

- Contoh bagaimana ?

·

Pipeline enam tahap dapat mengurangi waktu eksekusi 9 buah instruksi dari

54 satuan waktu menjadi 14 satuan waktu

- Bagaimana gambar prosesnya ?

·

Faktor menghambat peningkatan kinerja

?

- Keenam tahapan

memiliki durasi yang tidak sama, terjadi waktu tunggu pada beberapa tahapan

pipeline

- Instruksi

pencabangan bersyarat, yang dapat mengagalkan beberapa pengambilan instruksi

Contoh “Branch”

Rancangan Pipeline IBM S/360

- Ada 2 faktor

hambatan, yaitu:

-Masih terjadi

sampai sekarang

- Setiap tahapan

pipeline terdapat sejumlah overhead yang terjadi pada pemindahan data dari

buffer ke buffer dan pada saat melakukan persiapan dan pengiriman fungsi –

fungsi. Overhead akan memperpanjang waktu eksekusi instruksi tunggal.

Pertambahan waktu ini akan makin terasa apabila instruksi saling tergantung

secara logika

- Jumlah kontrol

logika yang diperlukan untuk menangani ketergantungan memori dan register akan

meningkat seiring banyaknya tahapan. Hal ini menyebabkan kerumitan dan waktu

fungsi pengontrolan

Penanganan Pencabangan

- Untuk apa ?

- Menjamin terjadinya

aliran instruksi yang stabil

- Kestabilan akan

terganggu saat instruksi mengalami pencabangan karena belum bisa ditentukan

tujuan pencabangan tersebut

- Beberapa metode

pendekatan masalah digunakan untuk mengatasi hal tersebut ?

Teknik pendekatan

1. Multiple

Streams

2. Prefetch branch target

3. Loop buffer

4. Branch prediction

5. Delayed branch

2. Prefetch branch target

3. Loop buffer

4. Branch prediction

5. Delayed branch

1. Multiple Streams

-Kedua instruksi

percabangan diambil dengan dua buah stream.

Kelemahan :

-Adanya persaingan

dalam mengakses register dan memori untuk dimasukkan dalam pipeline.

-Bila dalam

percabangan terdapat percabangan percabangan lagi, tidak mampu ditangani oleh

dua stream.

-Walaupun terdapat

kelemahan tapi terbukti meningkatkan kinerja kinerja pipelining.

·

Teknik Teknik ini ini diterapkan diterapkan pada pada IBM 370/168 IBM

370/168 dan IBM 3033 IBM 3033

2. Prefetch branch target

- Apabila pencabangan

bersyarat telah diketahui Prosesnya :

-Dilakukan

pengambilan awal (prefetch) terhadap instruksi setelah pencabangan dan target

pencabangan.

Diterapkan pada IBM 360/91.

-Diperlukan buffer

dan register untuk prefetch.

3. Loop buffer

-Apabila terdapat

pencabangan maka perangkat keras memeriksa apakah target pencabangan telah ada

dalam buffer, bila telah ada maka instruksi berikutnya diambil dari buffer.

- Perbedaan dengan

prefetch adalah pada loop buffer akan membuffer instruksi ke depan dalam jumlah

yang banyak, sehingga bila target tidak berjauhan lokasinya maka secara secara

otomatis telah terbuffer.

-Terkesan teknik ini

seperti cache memori, namun terdapat perbedaan karena loop buffer masih

mempertahankan urutan instruksi yang diambilnya.

4. Branch prediction

- Penganalisaan

sejarah instruksi. Kenapa ?

- Instruksi komputer

seringkali terjadi berulang.

Sehingga :

- Teknik prediksi ini

juga diterapkan dalam pengambilan instruksi pada cache memori.

- Diperlukan

algoritma khusus untuk melakukan prediksi tersebut.

- Patokan memprediksi

target pencabangan

· Penganalisaan eksekusi – eksekusi yang telah terjadi dan aspek lokalitas.

· Aspek lokalitas memori adalah kecenderungan penyimpanan instuksi yang

berhubungan dalam temapat yang berbeda.

5. Delayed branch

- Eksekusi pada

tahapan yang melibatkan pencabangan akan akan dilakukan penundaan proses

beberapa saat sampai didapatkan hasil pencabangan.

- Namun tahapan

pipelining lainnya dapat berjalan seiring penundaan tersebut.

- Teknik penundaan

ini menggunakan instruksi NOOP

Diagram alir prediksi

Penanganan Interupsi

- Interupsi adalah

fasilitas yang disediakan untuk mendukung sistem operasi

- Pengolahan

interupsi memungkinkan suatu program aplikasi dapat ditahan, agar kondisi –

kondisi insterupsi dapat dilayani, kemudian program dilanjutkan. .

- Interupsi adalah

suatu masalah dalam pipeline, karena mengganggu aliran instruksi yang telah

tersusun.

- Hal yang sering

dilakukan dalam perancangan adalah interupsi ditangguhkan beberapa saat sampai

program utama mendapatkan titik pemberhentian.

- Hal ini efektif

dilakukan sehingga tidak terlalu mengganggu pipelining instruksi

Diagram alir penanganan

Interupsi

Ada 2 macam :

1. Interupsi

yang dilakukan oleh perangkat keras

2. Interupsi

dari program (Exception)

Kesimpulan

Ø Syarat agar bisa disebut CPU adalah bisa mengambil instruksi, menterjemahkan, mengambil data, mengolah dan menyimpan kembali.

Ø CPU dibantu memori internal yang disebut register Terdapat dua group register yaitu register yang dapat diakses oleh programer (user visible register) dan register yang tidak bisa bisa diakses oleh programer (control status word).

Ø Siklus instruksi terdiri dari fetch, execute fetch, dan interupt

Ø Dengan cara pipelining kinerja CPU dapat ditingkatkan

Kesimpulan

Ø Syarat agar bisa disebut CPU adalah bisa mengambil instruksi, menterjemahkan, mengambil data, mengolah dan menyimpan kembali.

Ø CPU dibantu memori internal yang disebut register Terdapat dua group register yaitu register yang dapat diakses oleh programer (user visible register) dan register yang tidak bisa bisa diakses oleh programer (control status word).

Ø Siklus instruksi terdiri dari fetch, execute fetch, dan interupt

Ø Dengan cara pipelining kinerja CPU dapat ditingkatkan

ConversionConversion EmoticonEmoticon